The Intel Skull Canyon NUC6i7KYK mini-PC Review

by Ganesh T S on May 23, 2016 8:00 AM ESTGaming Benchmarks

Intel's Iris Pro Graphics SKUs with integrated EDRAM are amongst the highest-performing iGPUs in the market right now. The Core i7-6770HQ is equipped with Intel Iris Pro Graphics 580 - a GT4e part with 72 EUs and 128MB of eDRAM.

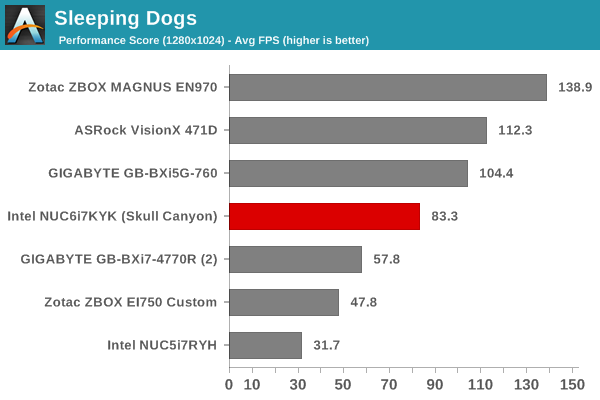

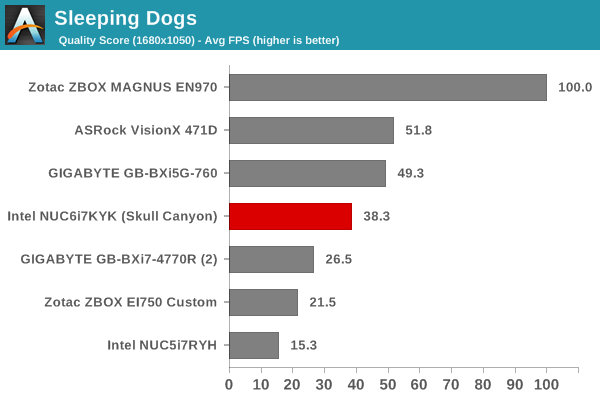

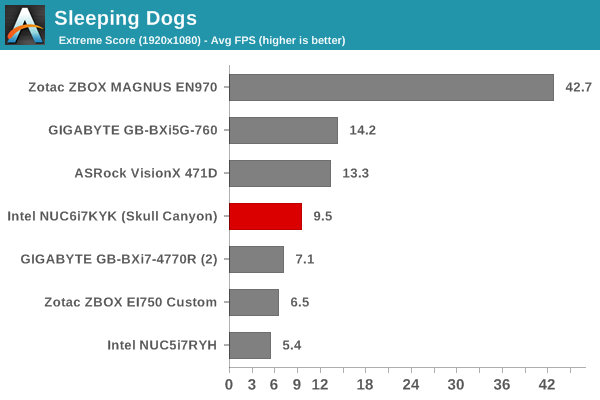

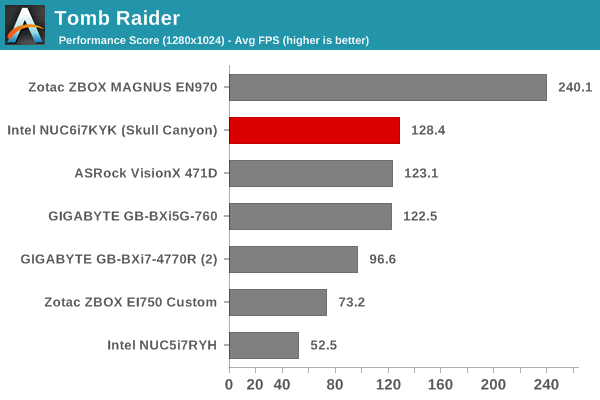

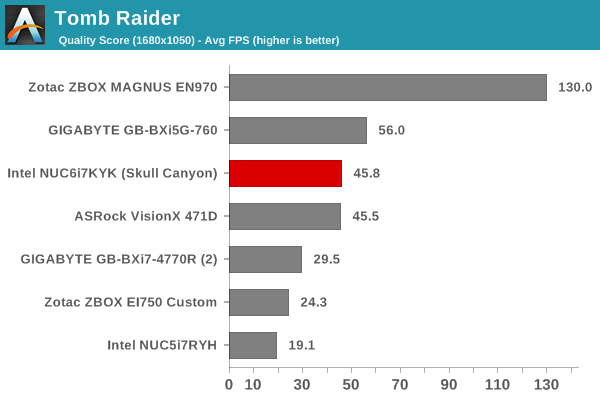

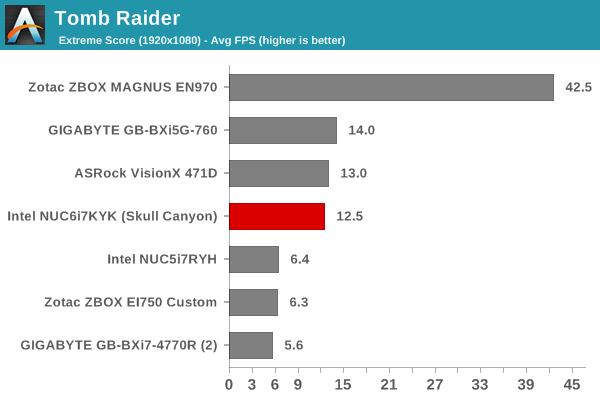

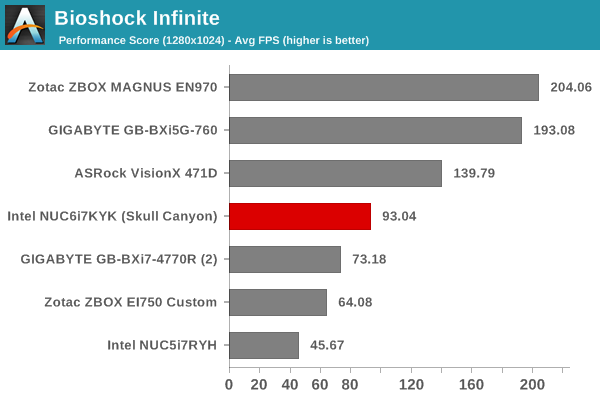

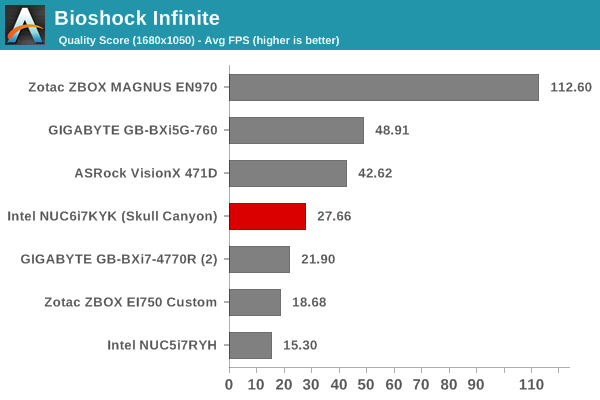

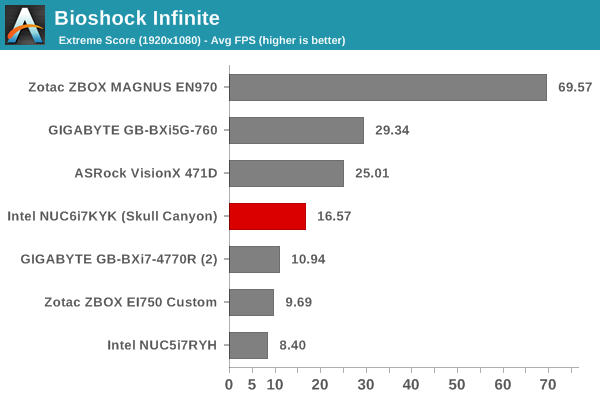

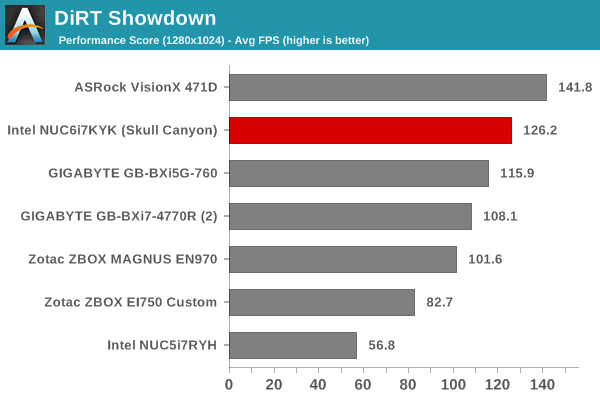

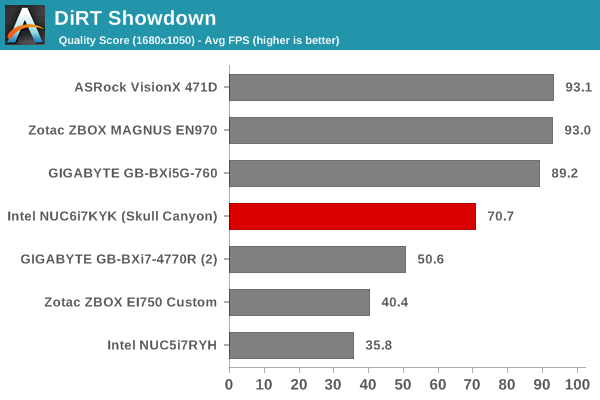

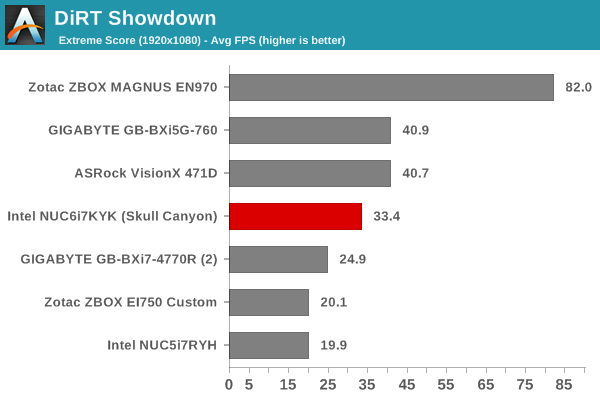

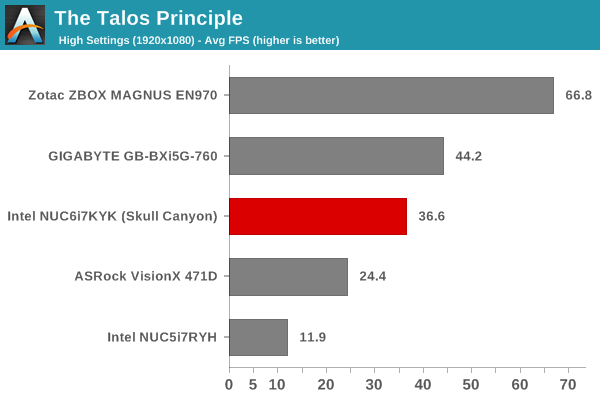

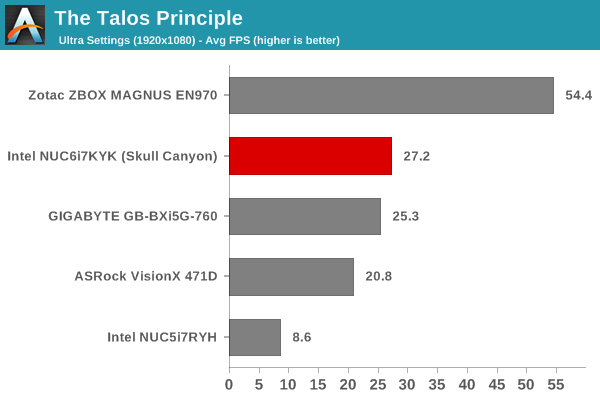

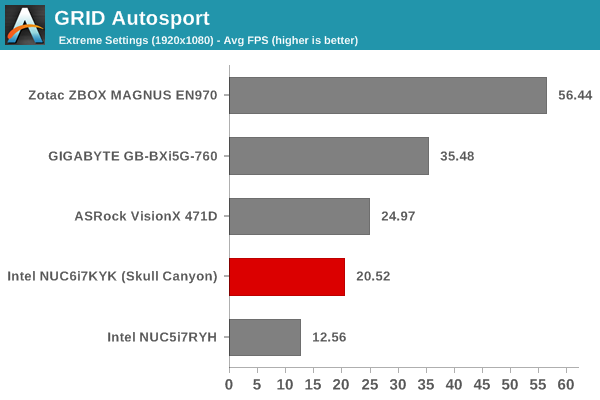

For the purpose of benchmarking, we chose six different games (Sleeping Dogs, Tomb Raider, Bioshock Infinite, The Talos Principle, GRID Autosport and DiRT Showdown) at various quality levels. The purpose of this section is not to benchmark the latest and greatest games, or benchmark at 4K resolutions. Intel clearly targets the Skull Canyon NUC towards casual gamers and those wanting to get introduced to mainstream gaming titles. As such, it is expected that people would play games with medium settings at 1080p or lower resolutions.

Sleeping Dogs

Tomb Raider

Bioshock Infinite

DiRT Showdown

The Talos Principle

GRID Autosport

All the numbers point to expected results - Skull Canyon is simply the best when it comes to having the best iGPU for gaming purposes. However, it is a bit of a disappointment when compared to systems having slightly bigger footprints, but, equipped with previous generation discrete mobile GPUs. An external Thunderbolt GPU dock can solve some of the issues for users wanting more graphics prowess than what the Iris Pro Graphics 580 can deliver, but that has a significant price premium, and it is not something that we evaluated as part of this review.

133 Comments

View All Comments

utferris - Monday, May 23, 2016 - link

This can be better with ECC memory support. I just can not use any machine without ECC for work.ShieTar - Monday, May 23, 2016 - link

But a low-frequency consumer quad-core is fine? What exactly do you do at work?Gigaplex - Tuesday, May 24, 2016 - link

Sometimes reliability is more important than performance.close - Monday, May 23, 2016 - link

Guess ECC is not high on the list for potential NUC buyers, even if it's a Skull Canyon NUC. I think most people would rather go for better graphics than ECC.kgardas - Monday, May 23, 2016 - link

Indeed, the picture shows SO-DIMM ECC, but I highly doubt this is even supported since otherwise it's not Xeon nor Cxxx chipset...close - Tuesday, May 24, 2016 - link

http://ark.intel.com/search/advanced?ECCMemory=tru...tipoo - Monday, May 23, 2016 - link

What work do you want to do on a 45W mobile quad with (albeit high end) integrated graphics, that needs ECC?I wonder how that would work with the eDRAM anyways, the main memory being ECC, but not the eDRAM.

Samus - Monday, May 23, 2016 - link

All of the cache in Intel CPU's is ECC anyway. Chances of errors not being corrected by bad information pulled from system RAM is rare (16e^64) in consumer applications.ECC was more important when there was a small amount of system RAM, but these days with the amount of RAM available, ECC is not only less effective but less necessary.

I'm all for ECC memory in the server/mainframe space but for this application it is certainly an odd request. This is, for the most part, a laptop without a screen.

TeXWiller - Tuesday, May 24, 2016 - link

>ECC was more important when there was a small amount of system RAM,The larger the array the larger target it is for the radiation to hit. Laptops are often being used in high altitude environments with generally less shielding than the typical desktop or even a server so from that perspective ECC would seem beneficial basic feature. Then there are the supercomputers, a fun read: http://spectrum.ieee.org/computing/hardware/how-to...

BurntMyBacon - Tuesday, May 24, 2016 - link

@TeXWiller: "The larger the array the larger target it is for the radiation to hit."While this is true, transistor density has improved to the point that, despite having magnitudes more capacity, the physical array size is actually smaller. Of course the transistors are also more susceptible given the radiant energy is, relatively speaking, much greater compared to the energy in the transistor than it was when transistors were larger. There is also the consideration that as transistor density increases, it becomes less likely that radiation will strike the silicon (or other substrate), but miss the transistor. So we've marginally decreased the chance that radiation will hit the substrate, but significantly increased the change that any hit that does occur will be meaningful.